- 您现在的位置:买卖IC网 > Sheet目录3841 > PIC16F737-I/SP (Microchip Technology)IC PIC MCU FLASH 4KX14 28DIP

2009 Microchip Technology Inc.

DS39636D-page 113

PIC18F2X1X/4X1X

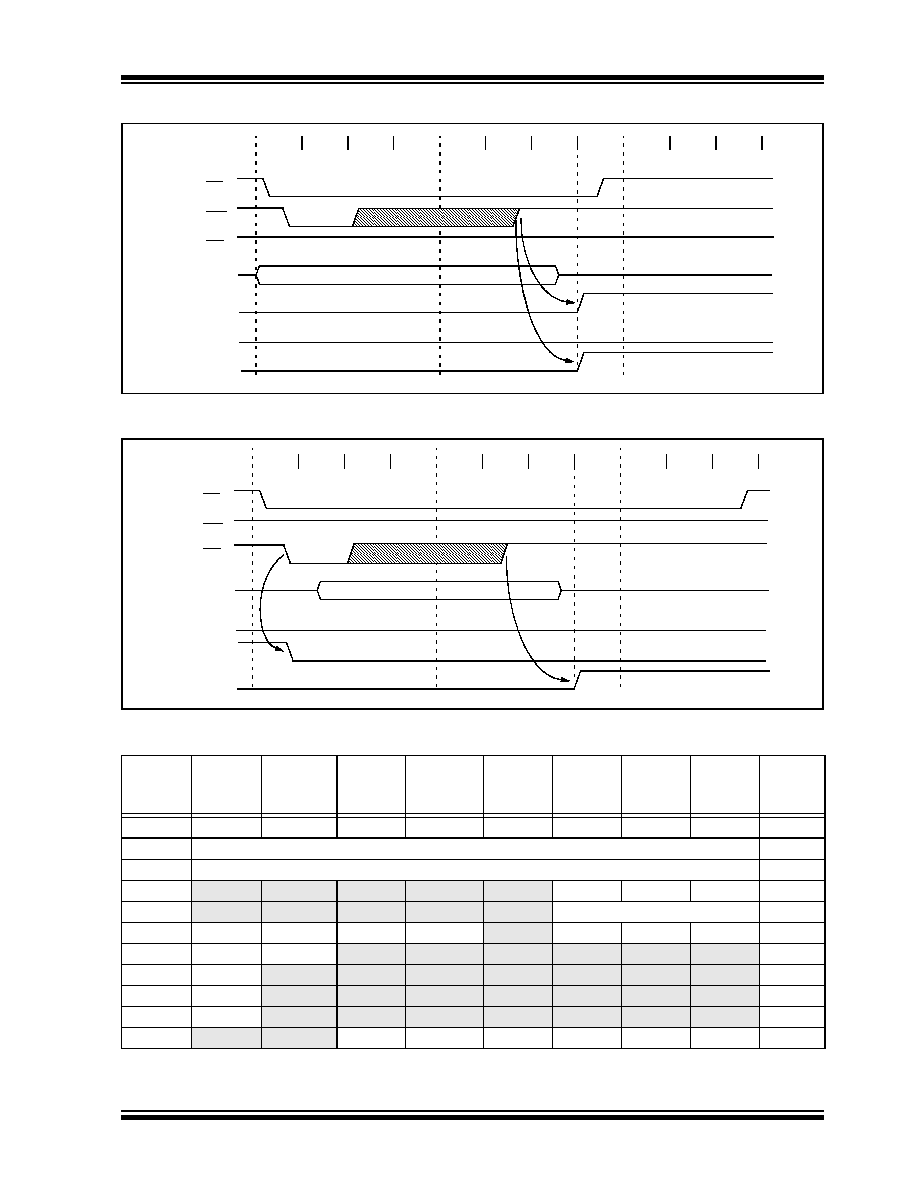

FIGURE 9-3:

PARALLEL SLAVE PORT WRITE WAVEFORMS

FIGURE 9-4:

PARALLEL SLAVE PORT READ WAVEFORMS

TABLE 9-11:

REGISTERS ASSOCIATED WITH PARALLEL SLAVE PORT

Name

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Reset

Values

on page

PORTD

RD7

RD6

RD5

RD4

RD3

RD2

RD1

RD0

LATD

PORTD Data Latch Register (Read and Write to Data Latch)

TRISD

PORTD Data Direction Control Register

PORTE

—

RE3

RE2

RE1

RE0

LATE

—

LATE Data Output bits

TRISE

IBF

OBF

IBOV

PSPMODE

—

TRISE2

TRISE1

TRISE0

INTCON

GIE/GIEH PEIE/GIEL

TMR0IF

INT0IE

RBIE

TMR0IF

INT0IF

RBIF

PIR1

PSPIF(1)

ADIF

RCIF

TXIF

SSPIF

CCP1IF

TMR2IF

TMR1IF

PIE1

PSPIE(1)

ADIE

RCIE

TXIE

SSPIE

CCP1IE

TMR2IE

TMR1IE

IPR1

PSPIP(1)

ADIP

RCIP

TXIP

SSPIP

CCP1IP

TMR2IP

TMR1IP

ADCON1

—

VCFG1

VCFG0

PCFG3

PCFG2

PCFG1

PCFG0

Legend: — = unimplemented, read as ‘0’. Shaded cells are not used by the Parallel Slave Port.

Note 1: These bits are unimplemented on 28-pin devices and read as ‘0’.

Q1

Q2

Q3

Q4

CS

Q1

Q2

Q3

Q4

Q1

Q2

Q3

Q4

WR

RD

IBF

OBF

PSPIF

PORTD<7:0>

Q1

Q2

Q3

Q4

CS

Q1

Q2

Q3

Q4

Q1

Q2

Q3

Q4

WR

IBF

PSPIF

RD

OBF

PORTD<7:0>

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC18F86K22-I/PTRSL

MCU PIC 64K FLASH XLP 80TQFP

PIC16C63A-04I/SP

IC MCU OTP 4KX14 PWM 28DIP

PIC16C63A-04I/SO

IC MCU OTP 4KX14 PWM 28SOIC

52559-2270

CONN FFC 22POS .5MM VERT ZIF SMD

52559-1870

CONN FFC 18POS .5MM VERT ZIF SMD

DSPIC33EP64MC506-I/PT

IC DSC 16BIT 64KB FLASH 64TQFP

52745-1896

CONN FFC 18POS .5MM R/A ZIF SMD

PIC16LC622-04/P

IC MCU OTP 2KX14 COMP 18DIP

相关代理商/技术参数

PIC16F737-I/SP

制造商:Microchip Technology Inc 功能描述:IC 8BIT FLASH MCU 16F737 SDIL28

PIC16F737-I/SS

功能描述:8位微控制器 -MCU 7KB 368 RAM 25 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F737T-I/ML

功能描述:8位微控制器 -MCU 7KB 368 RAM 25 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F737T-I/SO

功能描述:8位微控制器 -MCU 7KB 368 RAM 25 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F737T-I/SS

功能描述:8位微控制器 -MCU 7KB 368 RAM 25 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F73-E/ML

功能描述:8位微控制器 -MCU 7 KB 368 RAM 25I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F73-E/SO

功能描述:8位微控制器 -MCU 7KB 192 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F73-E/SP

功能描述:8位微控制器 -MCU 7KB 192 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT